p-ISSN: 2349-5804; e-ISSN: 2349-5812 Volume 4, Issue 3 April-June, 2017, pp. 98-102

© Krishi Sanskriti Publications

http://www.krishisanskriti.org/Publication.html

# Analysis and Design of Two Stage CMOS Operational Amplifier in 90nm CMOS Technology with High Gain and Low Power Dissipation

Gaurav Kr. Sharma<sup>1</sup>, Prerna Shukla<sup>2</sup> and Vijay Kr. Sharma<sup>3</sup>

<sup>1,2</sup>GLA University, Mathura

<sup>3</sup>Apex Institute of Engg, Jaipur

E-mail: <sup>1</sup>gaurav13sharma13@gmail.com, <sup>2</sup>prernashukla28@gmail.com, <sup>3</sup>vijay4everu@gmail.com

Abstract—The main concern in modern Integrated Circuit technology is given towards the power dissipation and gain of any electronic device for the applications where very small magnitude signals are to be processed. With the advancement of the CMOS technology, supply voltages are decreasing while at the same time the transistor threshold voltages are almost remaining constant. Operational Amplifier (Op-Amp) is widely known device for providing the high gain. In this paper two stage op-amp has been designed in 90nm technology. To maximize the gain, sizing of various transistors has been optimized. The designed two stage Op-Amp has gain of 46.037 db, phase margin of 66° and CMRR of 60db for 1pf load. It typically exhibits a 20MHz unity gain frequency for 25µA external bias current.

# 1. INTRODUCTION

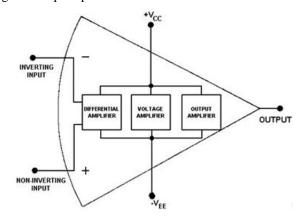

Today 's era the trend of low power low voltage silicon chip systems has been growing due to the increasing demand of portable and battery operated devices with smaller area and longer battery life time[1]. In analog electronics world the opamp plays a significant role. It has a linear characteristics, which is essential in almost all devices. Some of the applications of op-amps are in preamplifiers, buffers, voltage comparators and differential amplifiers, integration and differentiation [2]. At submicron levels the designing of such circuits becomes extremely difficult due to sensitivity of the circuit and trade off with various parameter[3].for faster speed, the supply voltage(vdd) is scaled down to enhance device reliability and to reduce power consumption, as the feature size of CMOS devices keeps shrinking. Higher transition frequency is obtained by downward scaling in gate length, and hence faster transistor's inherent open loop gain(gmro)[2][1].the threshold voltage of transistors does not scale well along with device scaling, which results the shrinking voltage headroom for the amplifier[2][1].In this paper two stage CMOS comparator has been simulated in 90nm CMOS technology for increasing the gain by changing the width of the transistors of circuit. In designing of op-amp, there is trade off between gain and bandwidth. The high gain is achieved by cascading, causes the reduction in the output signal swing[4] Along with gain the CMRR phase margin slew rate have been found out. Two stage op-amp is used to increase the gain of the circuit while another hand frequency compensation is needed for this circuit to make the system There are many techniques for frequency compensation, however single miller frequency compensation technique has been used in this circuit. Compensation techniques are generally robust and offer advantages such as: (i) pole splitting (ii) Left-half-plane(LHP) zero creation and its accurate placement through a null resistor. (iii)In the case of cascade compensation, eliminating the feed forward path due to the presence of a current buffer. Fig(1) shows the block diagram of op-amp.

Fig. 1: Block diagram of op-amp

This paper is organized as follows: In section II the description of two stage op-amp is discussed. Section III the designing procedure has been discussed with some equations.

In section IV simulated results are shown by some tables and our contribution is described.

## 2. CIRCUIT DESCRIPTION

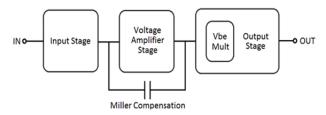

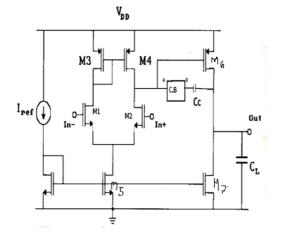

The two stage op-amp is most widely used architecture in ADC shown in figure(3). In which first stage consists of differential amplifier that will convert differential input voltage to differential current. At current mirror load this differential current are applied. Second stage consists of common source MOSFET, converting the second stage input voltage to current. The another transistor M7(current sink load) is used to convert a current to voltage at output node. Second stage is used to provide large swings. It performance and experimental results compare closely to the design specification .In single stage op-amp there is no need of frequency compensation with stable system but some applications required a high gain for that the stage of op-amp is increased. Increasing the stages makes the system unstable. To make the system stable along with high gain, single miller compensation technique has been used shown in figure (2).

Fig. 2: Single miller compensation technique

Fig. 3: Circuit diagram two stage open loop comparator.

## 3. CIRCUIT DESIGN PROCEDURE

The proposed circuit of two stage amplifier is Shown in figure(3). The design procedure of first stage as well as second stage of op-amp are,

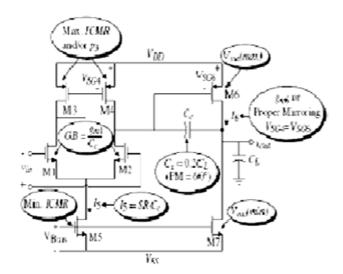

Fig. 4: Illustration of the design relationship and the circuit for a two stage op-amp

# Specifications-

Open loop gain (Av)

Minimum input common mode range(Vicm-)

Maximum input common mode range(Vicm+)

Load capacitance ( $C_I$ )

Output voltage swing

Swing rate

# Design steps-

Step(1) choose the value of  $C_L$  and will check later. This value must lie between 1pF and 2pF. This value of output capacitance of the first stage and the slew rate we can find the tail current or bias current ( $I_{\epsilon}$ ).

$$Cc >= 0.22C1$$

(1)

Step(2) Determine the value of the current I5 in transistor M5.

$$SR = I_5 / C_c$$

$$I_5 = C_c \times SR \tag{2}$$

Step(3) Design the transistor M1 and M2 by using the current calculated above.

$$(W/L)_{1,2} = \frac{g_{m1}^{2}}{\mu_{n}c_{ox}2I_{D1}}$$

(3)

Step(4) design the transistor M3 and M4 by choosing the value of (ICMR+) and finding out the value of Vt3max by using the cadence tool-

$$(W/L)_{3,4} = \frac{2I_{D3}}{\mu_p c_{ox} [V_{DD} - (ICMR+) - V_{t3\max} + V_{t1\min}]^2}$$

(4)

Step(5) Design the transistor M5 first calculate Vds5 using the specification of minimum input common mode voltage. The relation is given by

$$V_{Dsat} \ge ICMR \ (-) - \frac{2I_{D1}}{\beta_1} - V_{t1 \,\text{max}}$$

(5)

Using the above calculated value of vds5 we can design the transistor M5,

$$(W/L) = \frac{2I_{D5}}{\mu_n c_{or} (V_{Deat})'' 2}$$

(6)

Step(6) design transistor M6 by calculating the gm6 and gm4,for calculating gm6 consider the phase margin more than  $45^{\circ}$ , region being in two stage op-amp if the phase margin is lesser then 45 it will give ringing effect which makes the system unstable,

$$g_{m6} \ge 10g_{m1}$$

(7)

$g_{m4} = \sqrt{\mu_p c_{ox}(W/L).2I_D}$  (8)

$$(W/L)_6 = \frac{g_{m6}}{g_{m4}}(W/L)_4$$

(9)

Step(7) Design transistor  $M_7$ , first calculate the current  $I_6$

$$I_6 = I_7$$

$$\frac{I_6}{I_4} = \frac{(W/L)_6}{(W/L)_4} \tag{10}$$

$$\frac{I_7}{I_5} = \frac{(W/L)_7}{(W/L)_5} \tag{11}$$

## 4. SIMULATION RESULTS

TABLE I

**Design Specifications**

| S. No. | Parameters             | Value    |

|--------|------------------------|----------|

| 1.     | Open loop gain         | 46.037db |

| 2.     | Gain bandwidth product | 20Mhz    |

| 3.     | ICMR(+)                | 0.8v     |

| 4.     | ICMR(-)                | 0.5v     |

| 5.     | Phase margin           | 60       |

| 6. | Slew rate        | 20v/u.sec |

|----|------------------|-----------|

| 7. | Load capacitance | 2pF       |

| 8. | Vdd              | 1v        |

TABLE II

## Values of w in reference circuit-

| Name  | W       |

|-------|---------|

| W 1,2 | 15u     |

| W 3,4 | 25u     |

| W 5   | 20u     |

| W 6   | 25u     |

| W 7   | 13.756u |

**TABLE III**

# Effect of width of transistors on gain

| $I_{dc}$ | $W_{1,2}$ | $W_{3,4}$ | $W_5$ | $W_6$ | $W_7$ | Gain  | Power           |

|----------|-----------|-----------|-------|-------|-------|-------|-----------------|

| (µA)     | (µm)      | (µm)      | (µm)  | (µm)  | (µm)  | (db)  | dissipation(µW) |

| 30       | 15        | 20        | 10    | 20    | 15    | 23.63 | 62.18           |

| 30       | 15        | 20        | 10    | 25    | 13.75 | 31.4  | 67.67           |

| 30       | 15        | 30        | 25    | 25    | 13.75 | 45.93 | 56.52           |

| 30       | 15        | 25        | 25    | 25    | 25    | 46.03 | 58.47           |

# Obtained value of gain-

Practical value of gain is 46db

Theoretical value of gain is 45.67db

Simulated circuit diagram of two stage of open loop comparator

#### Simulation result-

Fig. 5: two stage open loop comparator

Gain obtained-

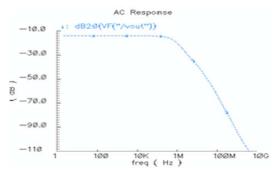

Gain obtained by simulation is 46.0317db. The upper graph (Fig6) shows the gain and lower graph shows the phase margin (Fig7).

Fig. 6: Open loop gain of Op-amp

Fig. 7: Phase margin of op-amp

**Power dissipation**-Power dissipation of whole circuit obtained is 59.9895u in 90nm CMOS technology.

Fig. 8: Power dissipation of whole circuit

# CMRR(common mode rejection ratio)-

Fig. 8: Common mode rejection ratio

## TABLE IV

Comparison of obtained simulation results after sizing in 90nm technology with 130nm and 180nm technology. Phase margin should be high to avoid ringing effect, obtained gain is enhanced as compare to previous work along with improved power dissipation.

| Parameter              | This Work | 90 nm  | 130nm  | 180nm |

|------------------------|-----------|--------|--------|-------|

| Open loop<br>gain (db) | 46.032    | 31     | 32     | 35.73 |

| Unity gain<br>BW (MHz) | 20        | 7.63   | 5.95   | 6.997 |

| Phase margin (deg)     | 66.22     | 75.287 | 75.007 | 75.50 |

## 5. CONCLUSION

In this paper a designing of two stage open loop comparator has been done to increase the gain of op-amp by varying the different transistor width. The gain obtained practically is 46.037db while actually it is 45.06db in 90nm technology at 20MhzGBW and power dissipation is 59.885u. The disadvantage of using two stage op-amp, it reduces the stability of device so to improve the stability a single miller compensation technique is used. The gain further can be improved by using the three stage or multiple stage in Op-Amp.

# REFERENCES

- [1] Amana yadav "Design of Two-stage CMOS Op-Amp and analyze the effect of scaling," international journal of engineering research and application(IJERA).vol2,issue 5, September-october 2012,pp.647-654.

- [2] Haresh s. Chaudhary and nilesh D. Patel et.al "Optimization and simulation of two stage operational amplifier using 180nm and 250nm technology," vol2, march-april 2013

- [3]H.C. chow and P.N. Weng, "A low voltage rail-to rail Op-amp design for biomedical signal filtering applications,"4<sup>th</sup> IEEE international symposium on electronic design,Test and application,pp.232-235,23-25 jan 2008.

- [4] Aldo pena perez and nithin kumar Y.B., "Slew rate and gain enhancement in two stage operational amplifier", university of paria via ferrater 1-27100-paria-ITALY.

- [5].Baker,R.J., CMOS: circuit design, Layout, and simulation. Revised 2<sup>nd</sup> Ed., wiley-IEEE, 2008.

- [6]sayan andyopadhyay and deep mukherjee et. Al, "Design of two stage CMOS operational amplifier in 180nm technology with low power and high CMRR", vol.11, june 2014.

- [7]vishal saxena and R.jacob Baker, "indirect compensation techniques for three stage op-amp," IEEE 2009.

- [8]Henil Langalia and sarthak Lad, "Analysis of two stage CMOS Op-amp for Single-Event Transients",ICCICT,oct 19-20,Mumbai,India

- [9]A.L.sternberg,L.W.Massengill,R.D.schrimpf,Y.Boulghassoul,H.J. Barnaby,S.Buchner,R.L.pease,and J.W.Howard, "Effect of amplifier parameters on single-event transients in an inverting operational amplifier,"IEEE Trans.onucl.sci,vol.49,no.3,p.p. 1-4,june2002.

- [10]K.N. Leung and P.K.T.Mok, "Nested miller compensation in low-power CMOS design," IEEE Trans. On circuits and system II,vol.48,no.4,pp.388-394,Apr2001.

- [11]K.N. Lenung and P.K.T. MOK, "analysis of multistage amplifier-frequency compensation, "IEEE trans.on circuit and systems I; vol.48,n0.9pp.1041-1056,sep 2001.

- [12]X. peng,w.sansen, "Transaconductance with capacitances feedback compensation for multistage amplifier", IEEE J. of solid state circuit,vol. 40, no.7 pp. 1514-1520, july 2005.

- [13]P.J. Hurst, "miller compensation using current buffer in fully differential cmos two stage operational amplifiers", IEEE Trans. On circuits and systems I: regular paper, vol.51, no.2, pp.245-285, feb.

- [14]P.R surkanti,A. Garimella,P.M. furth, "pole-zero analysis of multistage amplifiers: A tutorial overview, "2011 IEEE 54<sup>th</sup> international Midwest symposium on circuits and system, MWSCAS,pp.1,4,7-10 aug 2011.

- [15]B.K. Ahuja, "An improved frequency compensation technique for CMOS operational amplifiers", IEEE J. of solid state circuits, vol.18,no.6,pp.629-633,Dec 1983.